從零制作集成WiFi的單片機(jī) 所需知識(shí)與集成電路設(shè)計(jì)入門

從零開(kāi)始設(shè)計(jì)并制作一款集成WiFi功能的單片機(jī),是一個(gè)融合了硬件與軟件、數(shù)字與模擬、系統(tǒng)與模塊的復(fù)雜工程。這不僅需要深厚的理論知識(shí),還需要跨學(xué)科的實(shí)踐技能。以下是實(shí)現(xiàn)這一目標(biāo)所需的核心知識(shí)體系與集成電路設(shè)計(jì)的關(guān)鍵步驟。

第一部分:必備的基礎(chǔ)與專業(yè)知識(shí)

- 電子技術(shù)與電路基礎(chǔ)

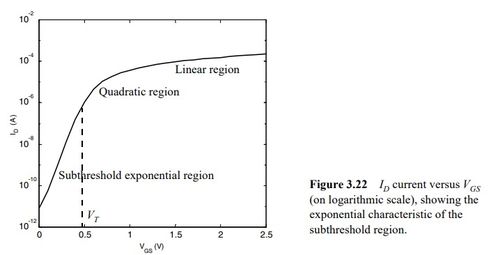

- 電路原理:深刻理解電阻、電容、電感、晶體管、MOS管等基本元件的特性與應(yīng)用。

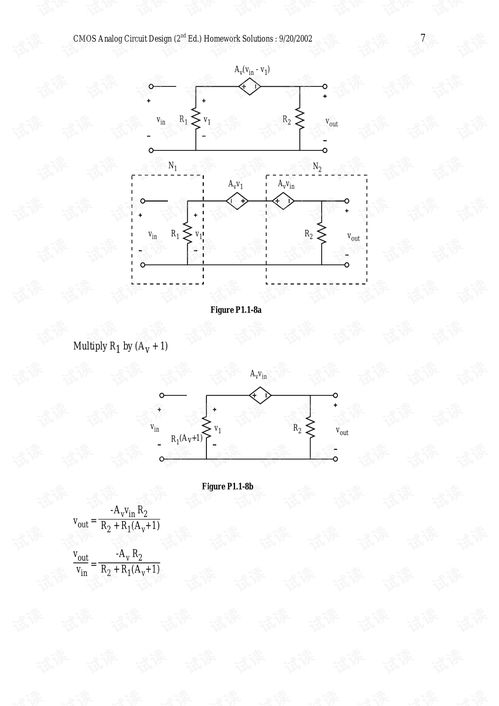

- 模擬電路:掌握放大器、濾波器、振蕩器、電源管理電路的設(shè)計(jì),這對(duì)處理WiFi射頻(RF)模擬信號(hào)至關(guān)重要。

- 數(shù)字電路:精通邏輯門、觸發(fā)器、寄存器、計(jì)數(shù)器、狀態(tài)機(jī)以及總線(如APB、AHB)的設(shè)計(jì),這是構(gòu)建CPU核心和數(shù)字外設(shè)的基石。

- 信號(hào)與系統(tǒng):理解信號(hào)的時(shí)域與頻域分析,為處理數(shù)字和無(wú)線信號(hào)提供理論基礎(chǔ)。

- 計(jì)算機(jī)體系結(jié)構(gòu)與嵌入式系統(tǒng)

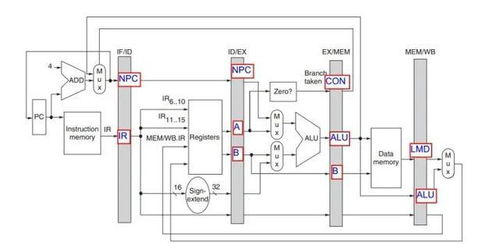

- CPU原理:深入了解馮·諾依曼/哈佛體系結(jié)構(gòu)、指令集架構(gòu)(如RISC-V、ARM Cortex-M)、流水線、中斷和存儲(chǔ)器層次結(jié)構(gòu)。

- 單片機(jī)原理:熟悉常見(jiàn)單片機(jī)(如STM32、ESP32)的架構(gòu),包括內(nèi)核、存儲(chǔ)器、時(shí)鐘系統(tǒng)及通用外設(shè)(GPIO、UART、SPI、I2C、ADC/DAC)。

- 嵌入式C語(yǔ)言/匯編語(yǔ)言:具備底層編程能力,能夠操作寄存器、管理內(nèi)存并優(yōu)化代碼效率。

- 無(wú)線通信與射頻(RF)知識(shí)

- WiFi協(xié)議棧:理解IEEE 802.11系列協(xié)議(物理層PHY和媒體接入控制層MAC),這是集成WiFi功能的直接依據(jù)。

- 射頻電路基礎(chǔ):學(xué)習(xí)天線原理、阻抗匹配、低噪聲放大器(LNA)、功率放大器(PA)、混頻器、濾波器等射頻前端電路的設(shè)計(jì)。

- 電磁兼容(EMC):了解如何減少芯片內(nèi)外的電磁干擾,確保無(wú)線通信的穩(wěn)定性和可靠性。

- 集成電路(IC)設(shè)計(jì)專用知識(shí)

- 硬件描述語(yǔ)言(HDL):精通Verilog或VHDL,用于進(jìn)行數(shù)字電路的行為級(jí)和寄存器傳輸級(jí)(RTL)設(shè)計(jì)。

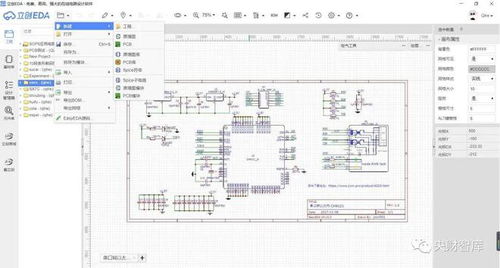

- EDA工具鏈:掌握使用行業(yè)標(biāo)準(zhǔn)工具(如Cadence、Synopsys系列)進(jìn)行仿真(ModelSim)、綜合(Design Compiler)、布局布線(IC Compiler)和物理驗(yàn)證。

- 半導(dǎo)體物理與工藝:了解CMOS等制造工藝的基本流程、器件物理特性(如閾值電壓、遷移率)以及工藝角(Corner)對(duì)設(shè)計(jì)的影響。

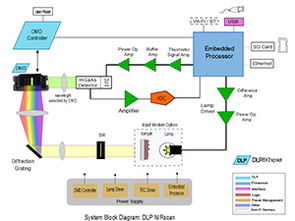

- 模擬/混合信號(hào)IC設(shè)計(jì):專門學(xué)習(xí)模擬電路在芯片上的實(shí)現(xiàn),包括運(yùn)放、PLL、ADC/DAC以及關(guān)鍵的WiFi射頻收發(fā)機(jī)模塊(如射頻前端、調(diào)制解調(diào)器)的設(shè)計(jì)。

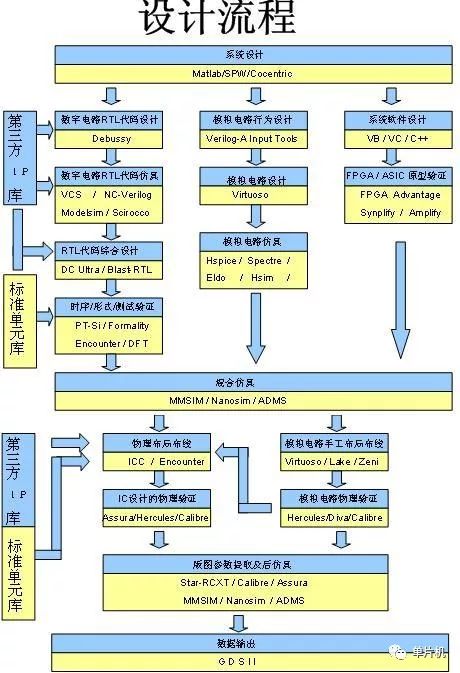

第二部分:集成電路設(shè)計(jì)流程概覽

從零設(shè)計(jì)這樣一款SoC(片上系統(tǒng))芯片,通常遵循以下流程:

- 系統(tǒng)架構(gòu)與指標(biāo)定義:明確芯片的具體規(guī)格,如CPU性能(主頻、位數(shù))、內(nèi)存容量、WiFi標(biāo)準(zhǔn)(802.11n/ac)、功耗預(yù)算、目標(biāo)工藝節(jié)點(diǎn)(如40nm、28nm)等。

- 模塊設(shè)計(jì)與RTL編碼:

- 數(shù)字部分:使用HDL設(shè)計(jì)CPU核心、數(shù)字外設(shè)控制器、MAC層硬件加速器等模塊。

- 模擬/射頻部分:使用專用工具進(jìn)行電路原理圖設(shè)計(jì)和仿真,完成WiFi射頻收發(fā)鏈、時(shí)鐘生成(PLL)、電源管理等關(guān)鍵模擬模塊。

- 前仿真與驗(yàn)證:利用測(cè)試平臺(tái)(Testbench)對(duì)RTL代碼進(jìn)行嚴(yán)格的功能驗(yàn)證和時(shí)序仿真,確保邏輯正確。

- 邏輯綜合:使用綜合工具將RTL代碼轉(zhuǎn)換為基于目標(biāo)工藝庫(kù)的門級(jí)網(wǎng)表,并進(jìn)行初步的時(shí)序和面積優(yōu)化。

- 物理設(shè)計(jì):

- 布局規(guī)劃:規(guī)劃芯片整體布局,放置核心模塊。

- 布線:完成模塊間以及模塊內(nèi)部所有信號(hào)線和時(shí)鐘線的連接。

- 特別關(guān)注:WiFi射頻部分需要特殊的隔離和屏蔽布局,以防止數(shù)字噪聲干擾敏感的模擬信號(hào)。

- 后仿真與驗(yàn)證:提取布局布線后的實(shí)際延時(shí)參數(shù),進(jìn)行更精確的時(shí)序仿真、功耗分析和電磁兼容性檢查。

- 流片與測(cè)試:將最終的設(shè)計(jì)數(shù)據(jù)(GDSII文件)交付給晶圓廠(如臺(tái)積電、中芯國(guó)際)進(jìn)行制造。芯片回來(lái)后,在專用測(cè)試平臺(tái)上進(jìn)行嚴(yán)格的硅后驗(yàn)證,包括WiFi功能、性能及可靠性測(cè)試。

第三部分:現(xiàn)實(shí)路徑與建議

需要清醒認(rèn)識(shí)到,“從零制作”對(duì)于個(gè)人或小團(tuán)隊(duì)而言,設(shè)計(jì)一款包含復(fù)雜射頻前端的商用級(jí)WiFi單片機(jī)是極其艱巨且成本高昂的(涉及數(shù)千萬(wàn)至上億的流片費(fèi)用)。更現(xiàn)實(shí)的入門和學(xué)習(xí)路徑是:

- 從FPGA開(kāi)始:使用FPGA平臺(tái)實(shí)現(xiàn)一個(gè)簡(jiǎn)單的軟核處理器(如開(kāi)源的RISC-V核)并集成數(shù)字外設(shè),這是學(xué)習(xí)數(shù)字IC設(shè)計(jì)流程的絕佳方式。對(duì)于WiFi功能,可以先使用現(xiàn)成的WiFi模塊(如ESP8266)通過(guò)SPI/SDIO與FPGA連接,理解協(xié)議交互。

- 利用開(kāi)源資源:積極參與如OpenCores、OpenHW Group等項(xiàng)目,研究開(kāi)源的CPU核(如Rocket Chip)、外設(shè)IP以及IEEE 802.11的開(kāi)源實(shí)現(xiàn)(如OpenWifi),在仿真環(huán)境中學(xué)習(xí)和修改。

- 分模塊深入學(xué)習(xí):不要試圖一口吃成胖子。可以分別深入數(shù)字IC設(shè)計(jì)、模擬IC設(shè)計(jì)(尤其是射頻IC)和嵌入式軟件系統(tǒng),再尋求系統(tǒng)集成。

從零打造集成WiFi的單片機(jī)是微電子與嵌入式系統(tǒng)領(lǐng)域的皇冠級(jí)挑戰(zhàn)。它要求設(shè)計(jì)者構(gòu)建一個(gè)從底層半導(dǎo)體物理到高層通信協(xié)議的完整知識(shí)金字塔。對(duì)于有志者而言,這是一個(gè)長(zhǎng)期而系統(tǒng)的學(xué)習(xí)旅程,建議從基礎(chǔ)學(xué)科扎實(shí)學(xué)起,循序漸進(jìn),并充分利用現(xiàn)代開(kāi)源工具和社區(qū)資源來(lái)降低實(shí)踐門檻。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.fucai3d68.cn/product/71.html

更新時(shí)間:2026-03-19 10:51:47